Interlaken is a royalty-free interconnect protocol that was developed by Cisco Systems and Cortina Systems in 2006. The full Interlaken protocol (described in the Interlaken Protocol Specification, v1.2) was designed to support chip-to-chip packet transfers in high-bandwidth networking equipment. A full Interlaken solution consists of the Interlaken Protocol Layer which runs on top of the Interlaken Framing Layer. The full Interlaken protocol is often viewed as too complex for designers who are looking for a lightweight, low-overhead way to connect multiple FPGAs, systems, or sensors. For these cases, the Interlaken Framing Layer provides everything needed for an extremely scalable, high-bandwidth, low-overhead and lightweight FPGA interconnect that supports any FPGA device family, each with a common user interface. The Interlaken Framing Layer is combined with the FPGA transceiver to form a complete IP core that we call the StreamDSP Interlaken-PHY IP Core. The Interlaken-PHY IP core can be used as the base upon which to build a more complex protocol or it can be used directly “out of the box” without modifications.

Features of the StreamDSP Interlaken-PHY IP Core:

- Channel bonding supported for any number of physical lanes

- Any serial line rate supported by the FPGA transceiver can be used

- Self-synchronizing links and automatic link resynchronization

- Per-lane CRC32 for data integrity and diagnostics

- Superb DC balancing for maximum link stability

- Over 95% bandwidth efficient

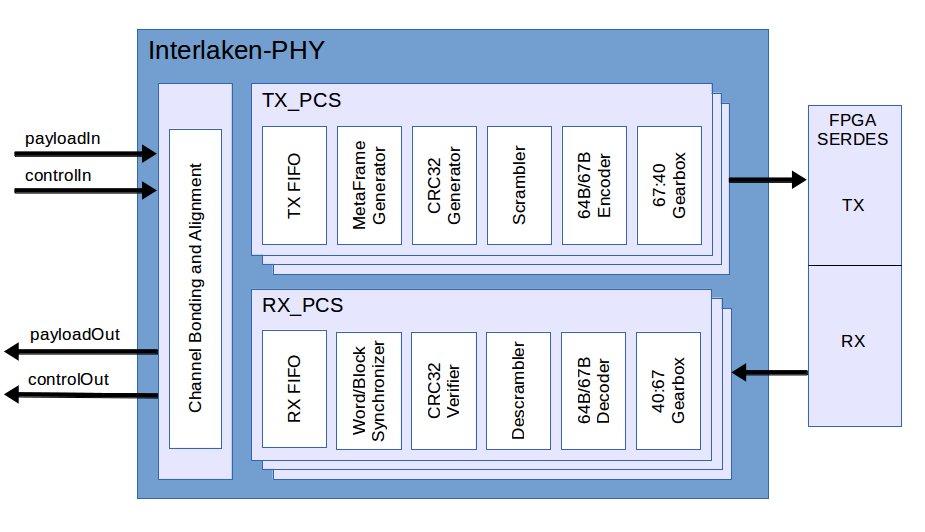

ILKN-PHY Core Block Diagram

FPGA Device Support

- Intel Agilex F-Tile – (including reference design for Intel Agilex I-Series FPGA Development Kit)

- Intel Agilex E-Tile – (including reference design for Intel Agilex F-Series FPGA Development Kit)

- Intel Stratix-10 – (including reference design for Intel Stratix-10 GX FPGA Development Kit (L-Tile and H-Tile))

- Intel Arria-10 – (including reference design for Intel Arria-10 GX FPGA Development Kit)

- Intel Cyclone-10 – (including reference design for Intel Arria-10 GX FPGA Development Kit)

- Altera Stratix-V GX – (including reference design for Altera Stratix-V GX FPGA Development Kit)

- Altera Stratix-IV GX (including reference designs for Altera Stratix-IV GX FPGA Development Kit)

- Altera Arria-V GX (including reference design for Altera Arria-V GX FPGA Starter Kit)

- Microsemi PolarFire (including reference design for Arrow Everest Development Board)

- Xilinx Alveo – (including reference design for Xilinx Alveo U200 Data Center Accelerator Card)

- Xilinx Versal ACAP GTY – (including reference design for Xilinx Versal AI Core Series VCK190 Evaluation Kit)

- Xilinx Versal ACAP GTM – (including reference design for Xilinx Versal Premium Series VPK120 Evaluation Kit)

- Xilinx Virtex UltraScale+ – (including reference design for Xilinx VCU118 Evaluation Kit)

- Xilinx Kintex UltraScale+ – (including reference design for Xilinx KCU116 Evaluation Kit)

- Xilinx Zynq UltraScale+ MPSoC – (including reference design for Xilinx ZCU102 Evaluation Kit)

- Xilinx Zynq UltraScale+ RFSoC – (including reference design for Xilinx ZCU111 Evaluation Kit)

- Xilinx Artix UltraScale+ – (including custom reference design with Xilinx XCAU25P Device)

- Xilinx Kintex UltraScale – (including reference design for Xilinx KCU105 Evaluation Kit)

- Xilinx Virtex UltraScale – (including reference design for Xilinx VCU108 Evaluation Kit)

- Xilinx Virtex-7 GTX (including reference design for Xilinx VC707 Dev Board)

- Xilinx Virtex-7 GTH (including reference design for Xilinx VC709 Dev Board)

- Xilinx Kintex-7 (including reference design for Xilinx KC705 Dev Board)

- Xilinx Artix-7 (including reference design for Xilinx AC701 Dev Board)

- Xilinx Virtex-6 LXT (including reference design for Xilinx ML605 Dev Board)

In addition to the devices listed above, support for any transceiver based FPGA from Intel (previously Altera), Microsemi, or Xilinx can be added in as little as 3-5 days with a valid user request.

StreamDSP’s multiple FPGA vendor support model provides customers extra flexibility and a low-overhead, high-bandwidth, SCALABLE data communication link between Altera, Intel, Microsemi and Xilinx FPGAs with a common user interface. The Interlaken-PHY IP core allows any number of channels to be bonded together for ultimate bandwidth flexibility. The IP can currently support any transceiver rate up to 32 Gbps, and a new development effort is underway to address link speeds up to 110+ Gbps in the newest FPGA devices. The Interlaken-PHY IP is designed to easily close timing even at the fastest transceiver rates and has an identical user interface for every FPGA family to ensure easy integration and design migration between families.

StreamDSP is committed to strong customer support, and will make every effort to ensure a successful IP integration. The FPGA IP core delivery includes a detailed User Guide, as well as “ready to run” demonstration designs for popular and easily available development boards. The demonstration designs each use a common data pattern generator and verifier circuit to allow any combination of development boards to be connected together to demonstrate error free communications as well as compatibility between Altera, Intel, Microsemi and Xilinx FPGAs. In addition to the demonstration designs, a complete self-verifying simulation testbench is provided that exercises the Interlaken-PHY IP Core in a stand-alone configuration.