sFPDP Gen3 (VITA 17.3) Release 4.1 now available!

This is a major release and recommended for all customers.

With Release 4.1, the StreamDSP sFPDP Gen 3 IP core now supports multi-stream transceivers with PAM4 data rates up to 116GB/s per lane in the latest FPGA devices like Versal and Agilex. Example designs have been updated to include 400G (4x100G), 100G (2x50G), and 50G (1x50G) links in FPGA devices that are capable of those rates.

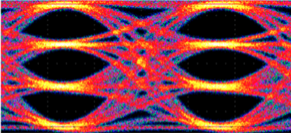

To improve bit-error-rates on high-speed PAM4 links, FEC can be implemented in all devices using the StreamDSP StreamFEC IP core.

In addition to PAM4 support, the v4.1 release contains the following improvements…

- Enabled support for multi-stream transceivers to support PAM4 rates

- Added option to perform automatic receive lane re-ordering (AUTO_ALIGN)

- Improved receive link synchronization logic in descrambler

- Improved xcvr_rx_reset output logic

- Changed recv_link_aligned output to recv_lane_misaligned for more info

- Removed redundant synchronizers in encoder and decoder

- Fixed bug in x_partial processing where duplicate flags could be sent

- Improved ramp_gen_check test logic to exercise partial flag processing

- Unified all example designs with common signal names and structure

- Added support for Altera Cyclone-V

- Improved example design description in documentation

- Updated all Altera designs to Quartus Pro 24.2

- Updated all Xilinx designs to Vivado 2024.2

- Updated all simulation scripts for Questa 2024.3_1

StreamDSP also offers custom design services…

– Create top-level custom sFPDP designs for you board (pinout verification, etc)

– Custom sFPDP integration work

– General FPGA design services also available

– Experienced FPGA designers with DSP, radar, comms, and video processing skills

– Email us at sales@streamdsp.com us for a quote!

See the full FEC press release here: