Serial Front Panel Data Port (Serial FPDP) is an industry standard, low-overhead, low-latency, high speed serial communication link defined by ANSI/VITA 17.1-2015. sFPDP is ideal for use in transceiver based FPGAs from Altera, Xilinx, and Microsemi to implement high-speed FPGA communication system backplanes, high-bandwidth remote sensor systems, FPGA signal processing, data recording, and high-bandwidth video systems. The low-overhead and simplistic nature of the protocol also makes it an attractive choice for replacement of parallel bus interconnects using modern transceiver technology. The StreamDSP sFPDP Core supports the full ANSI/VITA 17.1-2015 spec, including backward compatibility for older parallel FPDP bus architectures to allow for easy system upgrade.

StreamDSP is committed to supporting ALL FPGA vendors and device families, making sFPDP Gen3 a ubiquitous solution for high-speed serial interconnect. sFPDP Gen3 can replace existing proprietary protocols such as Aurora and SerialLite to provide a common user interface across all of your projects.

Features of the StreamDSP sFPDP IP Core include:

- VITA 17.1-2015 compliant

- Independent data/system clock domains

- 600 Mbps to 10+ Gbps serial rate support

- Optional flow control and CRC

- 32-bit user data interface

- Unidirectional and bidirectional support

- Optional link startup junk filtering

- All sFPDP frame types supported

- All sFPDP system configurations supported

- Multi-lane channel bonding wrapper

- Support for ALL transceiver-based FPGA device families

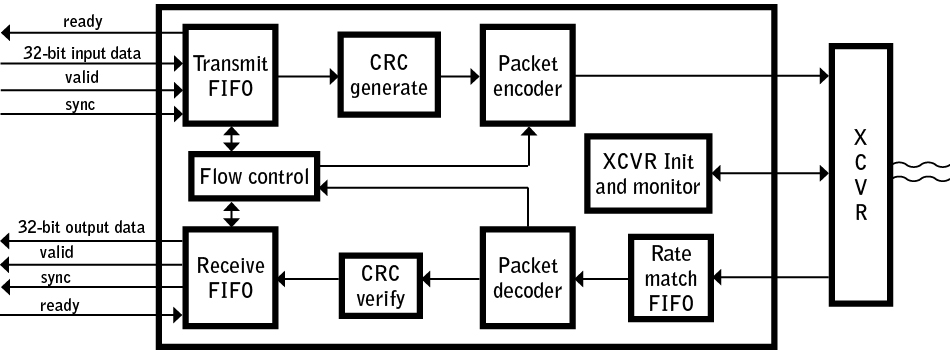

sFPDP Core Block Diagram

FPGA Device Support

- Intel Agilex F-Tile – (including reference design for Intel Agilex I-Series FPGA Development Kit)

- Intel Agilex E-Tile – (including reference design for Intel Agilex F-Series FPGA Development Kit)

- Intel Stratix-10 – (including reference design for Intel Stratix-10 GX FPGA Development Kit (L-Tile and H-Tile))

- Intel Arria-10 – (including reference design for Intel Arria-10 GX FPGA Development Kit)

- Intel Cyclone-10 – (including reference design for Intel Cyclone-10 GX FPGA Development Kit)

- Altera Stratix-V GX – (including reference design for Altera Stratix-V GX FPGA Development Kit)

- Altera Stratix-IV GX (including reference designs for Altera Stratix-IV GX FPGA Development Kit)

- Altera Stratix-II GX (including reference design for Altera Stratix-II GX PCI-Express Kit)

- Altera Arria GX (including reference design for Altera Arria GX PCI-Express Kit)

- Altera Arria-II GX (including reference design for Altera Arria-II GX FPGA Development Kit)

- Altera Arria-II GZ (including full simulation testbench and example designs)

- Altera Arria-V GX (including reference design for Altera Arria-V GX FPGA Starter Kit)

- Altera Arria-V GZ (including full simulation testbench and example designs)

- Altera Cyclone-IV GX (including reference design for Altera Cyclone-IV GX Transceiver Starter Kit)

- Altera Cyclone-V GX/SX/GT/ST (including reference design for Arrow/Terasic Cyclone-V SoCkit)

- Microsemi/Actel Igloo-2 (including reference design for Microsemi Igloo-2 Evaluation Kit)

- Microsemi PolarFire (including reference design for Arrow Everest Development Board)

- Xilinx Versal ACAP GTY – (including reference design for Xilinx Versal AI Core Series VCK190 Evaluation Kit)

- Xilinx Versal ACAP GTM – (including reference design for Xilinx Versal Premium Series VPK120 Evaluation Kit)

- Xilinx Virtex UltraScale+ – (including reference design for Xilinx VCU118 Evaluation Kit)

- Xilinx Kintex UltraScale+ – (including reference design for Xilinx KCU116 Evaluation Kit)

- Xilinx Zynq UltraScale+ MPSoC – (including reference design for Xilinx ZCU102 Evaluation Kit)

- Xilinx Zynq UltraScale+ RFSoC – (including reference design for Xilinx ZCU111 Evaluation Kit)

- Xilinx Artix UltraScale+ – (including custom reference design with Xilinx XCAU25P Device)

- Xilinx Kintex UltraScale – (including reference design for Xilinx KCU105 Evaluation Kit)

- Xilinx Virtex UltraScale – (including reference design for Xilinx VCU108 Evaluation Kit)

- Xilinx Virtex-7 GTX (including reference design for Xilinx VC707 Dev Board)

- Xilinx Virtex-7 GTH (including reference design for Xilinx VC709 Dev Board)

- Xilinx Kintex-7 (including reference design for Xilinx KC705 Dev Board)

- Xilinx Artix-7 (including reference design for Xilinx AC701 Dev Board)

- Xilinx Zynq-7000 GTX (including reference design for Xilinx Zynq-7000 SoC ZC706 Evaluation Kit)

- Xilinx Zynq-7000 GTP (including custom reference design for Xilinx Zynq-7000 FPGA)

- Xilinx Virtex-6 LXT (including reference design for Xilinx ML605 Dev Board)

- Xilinx Virtex-5 LXT (including reference design for Xilinx ML555 Dev Board)

- Xilinx Virtex-5 FXT (including reference design for Xilinx ML507 Dev Board)

- Xilinx Virtex-4 FX (including reference design for Xilinx ML405 Dev Board)

- Xilinx Spartan-6 LXT (including reference design for Xilinx SP605 Dev Board)

- Xilinx Virtex-2 Pro (including hardware tested reference design)

In addition to the devices listed above, we’d be happy to add support for any transceiver based FPGA from Intel (previously Altera), Xilinx, or Microsemi at your request! New device families, reference designs, simulations, etc can be added to our standard install in as little as 3-5 days.

This triple FPGA vendor support model gives our customers extra flexibility and provides a low-overhead, high-bandwidth data communication link between Altera, Xilinx, and Microsemi FPGAs with a common user interface. The sFPDP Core supports any of the standard sFPDP rates defined in VITA 17.1, but can also be configured for ANY transceiver rate supported by the FPGA up to 10+ Gbps on a single lane! This provides a scalable bandwidth solution for new products, and offers an attractive upgrade path for existing parallel sFPDP systems, custom backplanes, and high-speed interconnects.

For customers requiring even more bandwidth, we provide an easy-to-use multi-channel wrapper that allows several sFPDP lanes to be bonded together at the user FIFO level. This solution gives the user an interface that is identical to the single lane version but with a wider data bus (32*channels wide). The multi-lane wrapper also compensates for variation in the individual lane lengths and performs automatic synchronization between the lanes at the receiving end. This channel bonding wrapper is provided at no additional cost to the user, along with a channel bonding simulation.

We are committed to strong customer support, and will make every effort to ensure a successful sFPDP integration. The FPGA IP core delivery includes a detailed User Guide, as well as “ready to run” demonstration designs for popular and easily available development boards. The demonstration designs use an interactive terminal window to display sFPDP link status, and allows the user to change settings and run link integrity tests using either loopback or board-to-board configurations. In addition to the demonstration designs, we provide a complete self-verifying simulation testbench that exercises the sFPDP Core in a stand-alone configuration.

Development / Verification / Testing

We use Absolute Analysis’ Investigator™ series equipment to help us quickly develop, validate, and deploy our sFPDP IP. We use the Investigator™ system to generate random sFPDP traffic, inject bit errors, measure bit error rate, capture data, and serve as our sFPDP protocol analyzer during the development cycle. This development flow allows us to provide quick-turn reference designs to support new FPGA families and to quickly identify and correct any potential problems with the IP. Our customers rest assured knowing our IP is validated with the best sFPDP analyzer in the business!

In addition to the Absolute Analysis equipment, our IP has been sucessfully integrated with several other providers of sFPDP based equipment inluding:

- Conduant StreamStor data recorders

- VMETRO sFPDP data recorder

- Curtiss-Wright sFPDP data recorder

- Curtiss-Wright (Systran) Fibre-Xtreme sFPDP board