Serial Front Panel Data Port Gen3 (sFPDP-Gen3) is a VITA standard (VITA 17.3-2018 (R2025)) serial communications protocol for use in high bandwidth systems.VITA/ANSI 17.3 is the successor to the ANSI/VITA 17.1 standard and supports the same user data frame types and sync methods, allowing for easy user upgrades from VITA 17.1 to VITA 17.3. ANSI/VITA 17.3 standard was designed to be lightweight and low latency by using the 64B/67B framing layer defined by the Interlaken v1.3 specification, providing over 95% bandwidth efficiency! Multi-lane channel bonding and automatic lane synchronization allow for unprecedented bandwidth scalability.

StreamDSP is committed to supporting ALL FPGA vendors and device families, making sFPDP Gen3 (VITA 17.3) a ubiquitous solution for high-speed serial interconnect. sFPDP Gen3 can replace existing proprietary protocols such as Aurora and SerialLite to provide a common user interface across all of your projects.

The primary benefits of sFPDP-Gen3 include:

- New: Support for Lattice Avant G/X family

- New: Multi-stream transceiver support to enable PAM4 line rates up to 116 Gbps (per line)

- Hardware verified example designs using 400G (4x100G) links

- New: Forward Error Correction (FEC) support for all families using StreamFEC IP

- Separate license required for StreamFEC IP

- Virtex-6 not supported

- New: Automatic receive lane alignment for mis-wired links (optional)

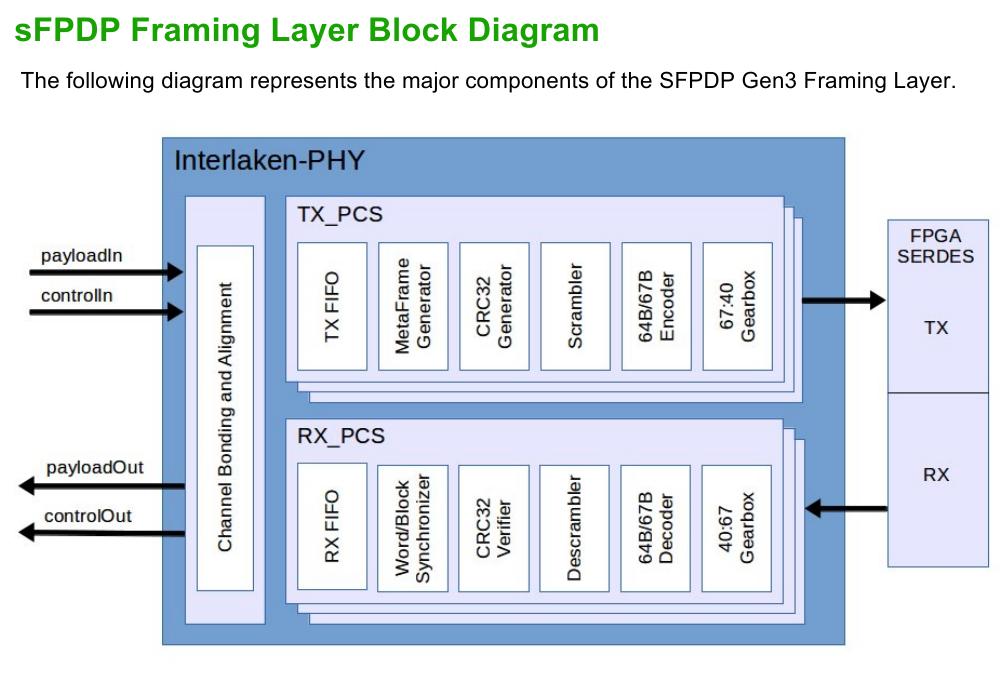

- Multi-lane channel bonding with advanced 64B/67B encoding

- Support for all legacy FPDP data framing types and sync methods

- New (optional) User Data Block (UDB) boundaries and per-UDB ID tags

- Per-lane CRC32 protection for framing layer

- CRC24 protection for all control words and UDB blocks

- Local and remote UDB Acknowledge feature allows for guaranteed transmission schemes

- Far-End link status information reports the health of the receive node

- Automatic lane/bundle synchronization

- Support for all transceiver line rates

- Support for any number of bonded channels

- Support for ALL transceiver-based FPGA device families

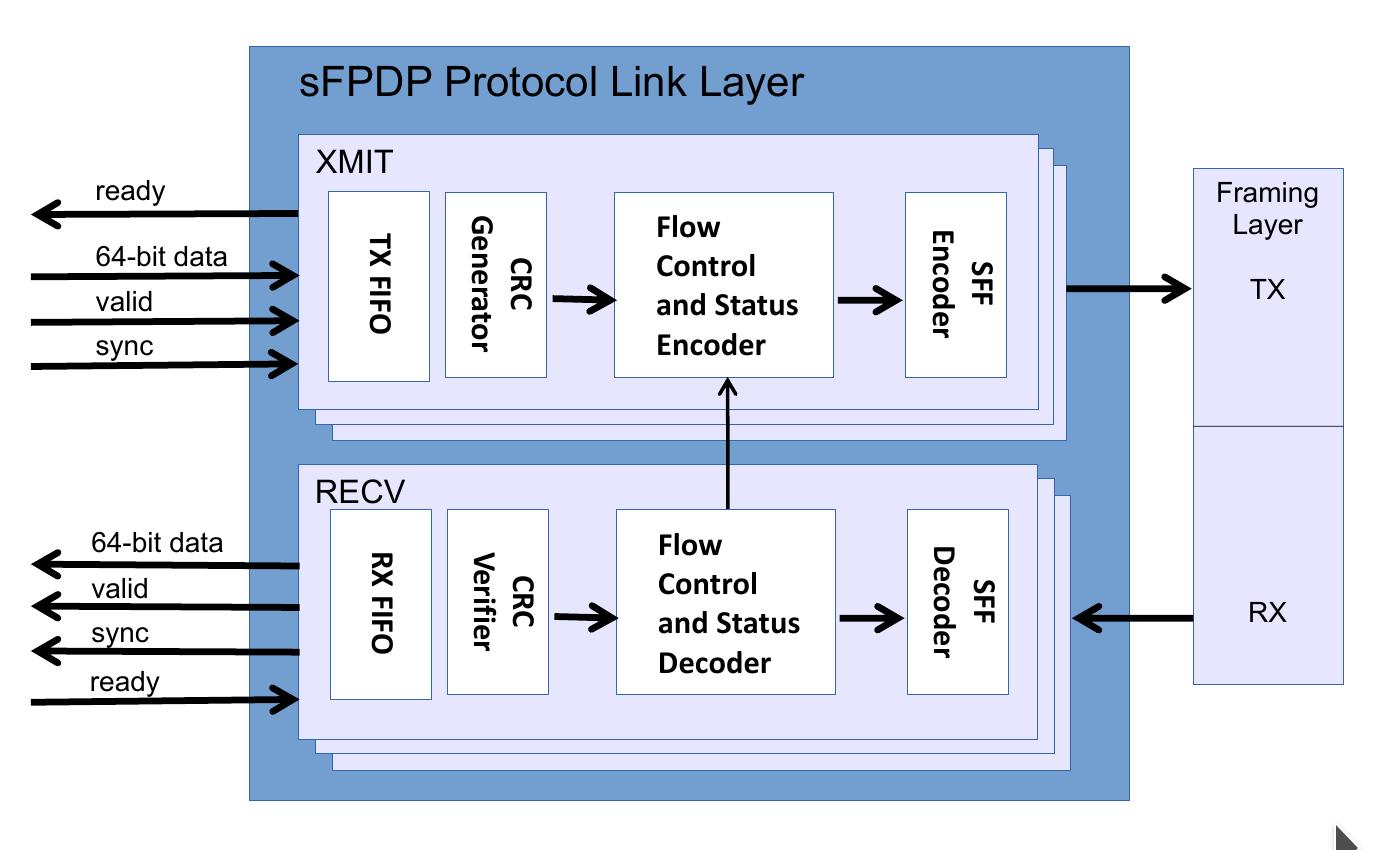

sFPDP Core Block Diagram

FPGA Device Support

- Intel Agilex F-Tile – (including reference design for Intel Agilex I-Series FPGA Development Kit)

- Intel Agilex E-Tile – (including reference design for Intel Agilex F-Series FPGA Development Kit)

- Intel Stratix-10 – (including reference design for Intel Stratix-10 GX FPGA Development Kit (L-Tile and H-Tile))

- Intel Arria-10 – (including reference design for Intel Arria-10 GX FPGA Development Kit)

- Intel Cyclone-10 – (including reference design for Intel Cyclone-10 GX FPGA Development Kit)

- Intel Cyclone-V GX/GT – (including reference design for Intel Cyclone-V GX FPGA Development Kit)

- Altera Stratix-V GX – (including reference design for Altera Stratix-V GX FPGA Development Kit)

- Altera Stratix-IV GX (including reference designs for Altera Stratix-IV GX FPGA Development Kit)

- Altera Arria-V GX (including reference design for Altera Arria-V GX FPGA Starter Kit)

- Microsemi PolarFire (including reference design for Arrow Everest Development Board)

- Lattice Avant G/X (including reference design for Lattice Avant-G/X Versa Board)

- Xilinx Alveo – (including reference design for Xilinx Alveo U200 Data Center Accelerator Card)

- Xilinx Versal ACAP GTY – (including reference design for Xilinx Versal AI Core Series VCK190 Evaluation Kit)

- Xilinx Versal ACAP GTM – (including reference design for Xilinx Versal Premium Series VPK120 Evaluation Kit)

- Xilinx Virtex UltraScale+ – (including reference design for Xilinx VCU118 Evaluation Kit)

- Xilinx Kintex UltraScale+ – (including reference design for Xilinx KCU116 Evaluation Kit)

- Xilinx Zynq UltraScale+ MPSoC – (including reference design for Xilinx ZCU102 Evaluation Kit)

- Xilinx Zynq UltraScale+ RFSoC – (including reference design for Xilinx ZCU111 Evaluation Kit)

- Xilinx Artix UltraScale+ – (including custom reference design with Xilinx XCAU25P Device)

- Xilinx Kintex UltraScale – (including reference design for Xilinx KCU105 Evaluation Kit)

- Xilinx Virtex UltraScale – (including reference design for Xilinx VCU108 Evaluation Kit)

- Xilinx Virtex-7 GTX (including reference design for Xilinx VC707 Dev Board)

- Xilinx Virtex-7 GTH (including reference design for Xilinx VC709 Dev Board)

- Xilinx Kintex-7 (including reference design for Xilinx KC705 Dev Board)

- Xilinx Artix-7 (including reference design for Xilinx AC701 Dev Board)

- Xilinx Virtex-6 LXT (including reference design for Xilinx ML605 Dev Board)

In addition to the devices listed above, we’d be happy to add support for any transceiver based FPGA from Intel (previously Altera), Xilinx, Microsemi, or Lattice at your request! New device families, reference designs, simulations, etc can be added to our standard install in as little as 3-5 days. This multiple FPGA vendor support model gives our customers extra flexibility – don’t be limited by your interconnect IP! The current VITA 17.3 sFPDP-Gen3 Core can support ANY transceiver rate up to 116 Gbps/line. This provides a scalable bandwidth solution for new products, and offers an attractive upgrade path for existing VITA 17.1 sFPDP systems, custom backplanes, and high-speed interconnects.

We currently have customers using our VITA 17.3 sFPDP Gen3 IP at rates ranging from single 2.5G channels up to 400G bonded channels. The 400G channels are implemented as 4x100G and have been hardware verified in the Agilex F-Tile development kit as well as the Versal VPK120 development kit (example designs available). The ability to support multiple FPGA vendors at any line rate and any number of bonded channels makes the StreamDSP sFPDP Gen3 IP core one of the most flexible and scalable solutions available on the market today.

We are committed to strong customer support, and will make every effort to ensure a successful sFPDP-Gen3 integration. The FPGA IP core delivery includes a detailed User Guide, as well as “ready to run” demonstration designs for popular and easily available development boards. The demonstration designs include example single-lane and multi-lane transceiver configurations to make your integration easy. In addition to the demonstration designs, we provide a complete self-verifying simulation testbench with ready-to-run scripts.